園區管理迎新利器 企業盒子智慧園區解決方案破解運營增效與運維難題

隨著園區運營日益復雜化,傳統管理方式難以應對效率與服務的雙重挑戰。企業盒子推出的智慧園區解決方案,以信息系統運行維護服務為核心,為園區管理注入全新活力,成為園區運營增效的有力工具。

一、智慧園區解決方案的核心優勢

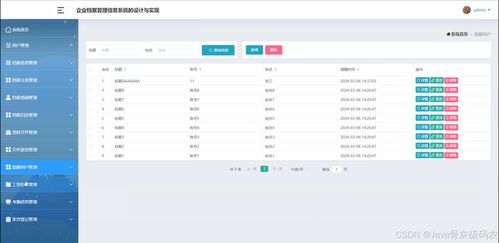

企業盒子智慧園區解決方案整合物聯網、大數據和云計算技術,構建統一的數字管理平臺。其優勢體現在:

- 運營效率提升:通過自動化流程和智能調度,減少人工干預,園區能耗、安防、停車等管理效率提高30%以上。

- 數據驅動決策:實時采集并分析園區運營數據,為管理者提供可視化看板和預警機制,助力精準決策。

- 服務體驗優化:集成門禁、報修、繳費等功能于一體,提升企業與員工的使用滿意度。

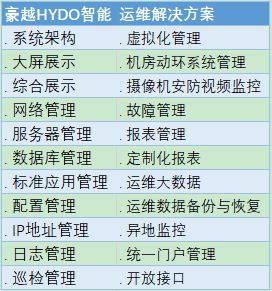

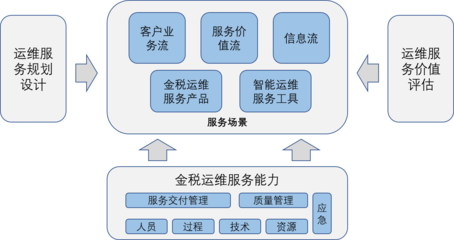

二、信息系統運行維護服務的關鍵作用

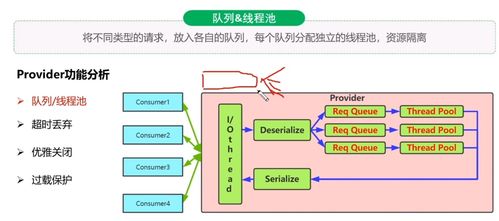

信息系統是智慧園區的“大腦”,其穩定運行至關重要。企業盒子提供全方位的運行維護服務:

- 預防性維護:定期巡檢與性能優化,提前發現并解決潛在問題,降低系統故障率。

- 快速響應支持:7×24小時監控與應急處理,確保系統高可用性,最小化停機時間。

- 安全與升級保障:實施網絡安全防護和定期軟件更新,適應業務變化與法規要求。

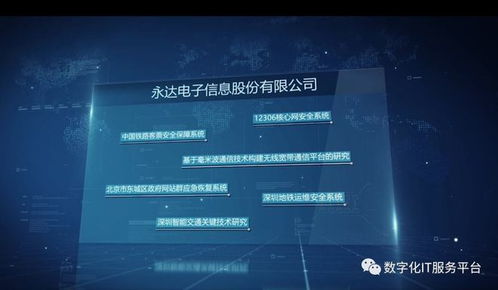

三、破解運營增效難題的實際案例

在某科技園區應用中,企業盒子解決方案幫助管理方實現了:

- 運營成本降低20%,通過智能能耗管理減少浪費;

- 服務響應時間縮短50%,依托移動端報修系統提升效率;

- 信息系統故障率下降70%,運維服務保障了業務連續性。

結語

企業盒子智慧園區解決方案不僅是一項技術升級,更是園區運營模式的革新。結合專業的運行維護服務,它為園區管理者破解了增效難題,打造了智能、高效、安全的現代化園區生態。隨著5G和AI技術的深度融合,這一方案將持續賦能園區數字化轉型。

如若轉載,請注明出處:http://www.vraynb.cn/product/45.html

更新時間:2026-03-18 01:43:21